# MINIMALIST: An Environment for the Synthesis, Verification and Testability of Burst-Mode Asynchronous Machines

Columbia University Computer Science Dept. Tech Report #CUCS-020-99

Robert M. Fuhrer\* Niraj K. Jha† Steven M. Nowick\*

Bill Lin‡

Michael Theobald\*

Luis Plana\*

\*Dept. of Computer Sci. Columbia University New York, NY 10027

†Dept. of Electrical Eng. Princeton University Princeton, NJ 08540 ‡Dept. of Elec. & Comp. Eng. Univ. of Calif. at San Diego La Jolla, CA 92093

July 26, 1999

#### Abstract

MINIMALIST is a new extensible environment for the synthesis and verification of burst-mode asynchronous finite-state machines. MINIMALIST embodies a complete technology-independent synthesis path, with state-of-the-art exact and heuristic asynchronous synthesis algorithms, e.g. optimal state assignment (CHASM), two-level hazard-free logic minimization (HFMIN, ESPRESSO-HF, and IMPYMIN), and synthesis-for-testability. Unlike other asynchronous synthesis packages, MINIMALIST also offers many options: literal vs. product optimization, single- vs. multi-output logic minimization, using vs. not using fed-back outputs as state variables, and exploring varied code lengths during state assignment, thus allowing the designer to explore trade-offs and select the implementation style which best suits the application. MINIMALIST benchmark results demonstrate its ability to produce implementations with an average of 34% and up to 48% less area, and an average of 11% and up to 37% better performance, than the best existing package [38]. Our synthesis-for-testability method guarantees 100% testability under both stuck-at and robust path delay fault models, requiring little or no overhead. MINIMALIST also features both command-line and graphic user interfaces, and supports extension via well-defined interfaces for adding new tools. As such, it is easily augmented to form a complete path to technology-dependent logic.

## 1 Introduction

While asynchronous circuits have undergone a renaissance driven by significant renewed interest in the last decade, their promises — reduced power, increased performance, and robustness — have only begun to be fully realized [38][6][21][16][29][15][18][31][19]. Although several of these methods have been effective, several synthesis steps still lack optimal solutions or practical tools. Likewise, a lack of well-integrated and extensible environments within which to embed these tools leaves designers without a smooth synthesis

<sup>\*</sup>This research was funded in part by NSF CAREER Award MIP-9501880, NSF RIA grant MIP-9308810, NSF grant CCR-97-34803, by a supplement to NSF MIP-9501880 for CAD software tool development and by an Alfred P. Sloan Research Fellowship.

path. By contrast, the synchronous community possesses a wealth of such tools and environments, both commercial and academic [10], which benefit both researchers and end-users.

Thus, MINIMALIST makes contributions on several fronts:

- An integrated synthesis path consisting of state-of-the-art asynchronous synthesis algorithms:

- Chasm, the first general optimal state encoding tool for asynchronous machines, providing both exact and fixed-length modes, and which can produce exactly-minimum output logic, a key parameter in asynchronous system performance

- Hfmin, the only exact hazard-free *symbolic* two-level logic minimizer, supporting both singleand multi-output implementations

- Impymin, a new *implicit* exact hazard-free two-level logic minimizer, capable of solving all available benchmark problems in under 15 minutes, including several previously unsolvable problems

- Espresso-HF, a very fast new heuristic hazard-free two-level logic minimizer, which typically produces optimal or near-optimal results in under 3 seconds

- Synthesis for testability, yielding 100%-testable multi-level implementations under either stuckat or robust path delay fault models, with little or no area overhead

- In contrast to existing synthesis paths, Minimalist provides a single synthesis path able to produce implementations in a variety of styles (e.g., single-output vs. multi-output, using vs. not using fed-back outputs as state variables, exploring various state code lengths) under various cost functions, allowing the exploration of design trade-offs

- The first complete and practical technology-independent synthesis path for burst-mode circuits using fast optimal algorithms

- An easily-usable environment with a software framework which can readily incorporate new tools

MINIMALIST currently supports widely-used plain burst-mode [22][32] specifications. Extended burst-mode specifications [42] will be supported in a forthcoming release.

## 2 Background and Overview

#### 2.1 Asynchronous Synthesis

Asynchronous controller synthesis follows a flow similar to that of synchronous synthesis; however, it presents unique problems requiring significantly different solution methods. Like synchronous synthesis, the synthesis trajectory is divided for tractability's sake into several steps: state minimization, state encoding, two-level logic minimization, multi-level transformation, synthesis for testability, and so on. Each of these steps can be modeled roughly after its synchronous counterpart, but poses additional complications. We now review each step, outlining the basic problems unique to asynchronous synthesis.

The task of *state minimization* is to find a minimum-cardinality closed state cover for the original burst-mode specification. The result is a reduced machine realizing the original specification [13]. As with synchronous machines, this problem can be solved by first forming a set of compatibles and then forming a binate covering problem expressing the two basic sets of constraints (coverage and closure) [12]. Asynchronous machines, however, require different forms of compatible in order to be assured of the existence of a hazard-free logic implementation [23].

State encoding produces a set of binary codes for the symbolic states of the reduced machine. For synchronous machines, all encodings which distinguish the states are valid; however, typically this is performed judiciously, so as to minimize logic area [9], improve performance, or reduce power consumption. By contrast, asynchronous machines must be encoded so as to avoid critical races [35]. Further, if optimal logic is to be obtained, logic hazards [36][24] must be taken into account [11].

Finally, to ensure correct operation, two-level logic minimization for burst-mode asynchronous machines must also take care to avoid logic hazards. Recent developments in this area include exact multi-valued-input (i.e., mvi)/multi-output minimization [11], fast heuristic minimization [33], and exact implicit minimization [34].

An additional issue facing asynchronous synthesis is the potential for using fed-back outputs to reduce the number of state variables and the overall implementation complexity. In this machine implementation style, primary outputs are fed back as additional input variables, which help to identify the machine's present state, thereby reducing the need for distinct state variables. The loading on the outputs may be minimal (only a short path to a feedback buffer is added to its fan-out), but the savings in overall logic complexity can be dramatic. Care must be taken, however, in various synthesis steps, in order to ensure that the use of fed-back outputs does not introduce hazards or critical races.

## 2.2 Burst-Mode Specifications

MINIMALIST addresses the class of asynchronous controller specifications known as *burst-mode*, a generalization of the traditional multiple-input change (MIC) mode [36]. Burst-mode was first formalized by Nowick [22], who also developed UCLOCK, a systematic synthesis method for hazard-free implementations. This specification style is based on more ad-hoc methods used earlier by Davis et al.. [8].

Burst-mode machines allow multiple inputs to change concurrently, but, unlike MIC machines, in any order and at any time. This relaxation considerably reduces the timing constraints placed on the environment, but nonetheless allows economical and high-performance implementations. In particular, applying Nowick's method for exact two-level hazard-free logic minimization [25] yields low-area, high-performance circuits.

Burst-mode has been successfully used by both academia and commercial interests to design and implement a number of significant circuits, for example, at Stanford, UCSD, HP, AMD and Intel.

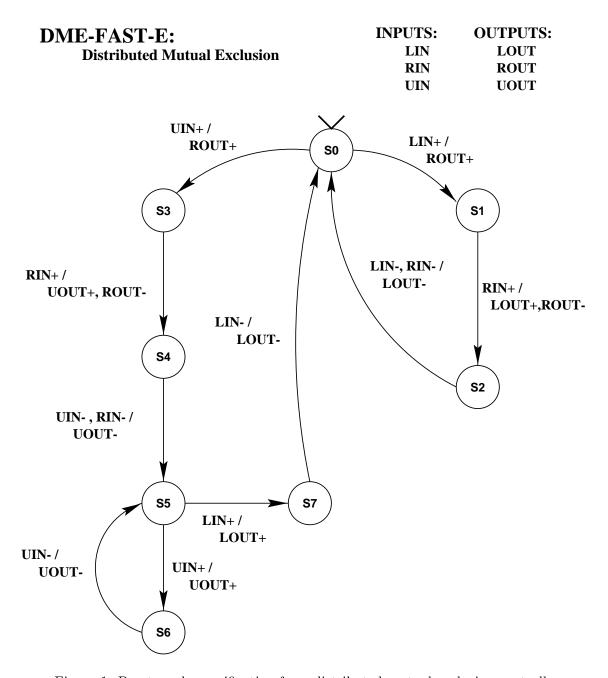

The specifications are most easily illustrated by example. A burst-mode specification for a distributed mutual-exclusion controller with 3 inputs and 3 outputs is shown in Figure 1. The unique starting state (SO) is indicated by a 'v', and initial input and output values are either explicitly specified or (as in the figure) default to 0. Each arc is labelled with a set of input and output transitions, known as *bursts*, separated by a '/'. Rising transitions are denoted by a '+'; falling transitions, by a '-'.

The operation of a burst-mode machine is as follows. Starting in a given state, the machine remains stable in that state until a complete input burst arrives. Individual inputs within that burst may arrive in any order and at any time. Once the last input arrives, the burst is complete. The machine then generates the corresponding output burst, if any, and moves to the specified next state. The environment allows the machine to settle, and the next cycle begins.

Figure 1 illustrates burst-mode operation. For example, consider the transition from S2 to S0, with corresponding input and output bursts LIN-,RIN- and LOUT-, respectively. As a result, when in S2, if the pair of input changes LIN- and RIN- arrive at any order, and within any time window, the machine responds with a falling edge on LOUT and a transition to S0.

Burst-mode specifications must obey two important restrictions. First, input bursts must not be empty; in the absence of input changes, the machine remains stable in its current state. Second, the so-called maximal set property stipulates that no arc leaving a given state may possess an input burst that is a subset of any other arc leaving that state. This property guarantees that, at all times, the machine can

Figure 1: Burst-mode specification for a distributed mutual-exclusion controller

```

name DME_FAST_E

input LIN 0

input RIN 0

input UIN 0

output LOUT 0

output ROUT O

output UOUT 0

LIN+

ROUT+

0.3

UIN+ I

ROUT+

1 2

RIN+

LOUT+ ROUT-

2.0

LIN- RIN- | LOUT-

RIN+

UOUT+ ROUT-

UIN- RIN- | UOUT-

4 5

UIN+

UOUT+

5 7

LIN+ |

LOUT+

6 5

UIN- I

UOUT-

7 0

LIN-

LOUT-

```

Figure 2: Textual (.bms) burst-mode specification for DME-FAST-E

unambiguously decide whether to follow a transition or remain stable.

It is important to understand that, in a given burst-mode specification, any unspecified input combinations are forbidden. For example, the input burst RIN+ in state SO in the specification of Figure 1 is prohibited. In other words, the surrounding circuitry must never generate that input combination. Any such combinations can thus be treated as don't-cares, and used to optimize the machine's implementation.

It is also conventional to adhere to a simple constraint, in order to ensure that the burst-mode specification can be properly synthesized<sup>1</sup>. Each state must have a *unique entry point*, i.e., a unique set of input and output values upon entry. In other words, each state has a *single* total state that is the destination of one or more transitions. Note that this property is not necessary for proper burst-mode operation. However, it tends to produce machines which are more easily minimized, and which are more easily proven to have hazard-free implementations.

An equivalent textual burst-mode specification (as used by MINIMALIST and MEAT [7]) appears in Figure 2, and an equivalent flow table in Figure 3.

It is easy to see from Figure 3 that burst-mode specifications frequently offer significant opportunity for state minimization. This due to the unique entry point criterion, which generally results in states which bind the output and next-state functions in only a few input columns.

#### 2.3 Previous Work

We now briefly review two previous burst-mode asynchronous synthesis systems, and compare them to MINIMALIST.

The UCLOCK [23] system is a nearly complete path from plain burst-mode specifications to two-level logic. It incorporates a safe, exact state minimization algorithm, and the first exact hazard-free single-output logic minimization algorithm [24]. Unlike MINIMALIST, however, it offers no automated method for

<sup>&</sup>lt;sup>1</sup>This is in fact a sufficient, but not necessary, constraint.

```

Inputs: LIN, RIN, UIN;

Outputs: LOUT, ROUT, UOUT;

#Sn:

000

001

011

010

110

111

101

100

S0,000 S3,010

-,---

-,---

-.---

S0:

-,--- S1,010;

S1:

-,--- S2,100 -,---

-, --- S1,010;

S2:

-,--- S2,100 S2,100

-,---

S3:

-,--- S3,010 S4,001 -,--- -,---

$5,000 $4,001 $4,001 $4,001 -,---

S4:

S5,000 S6,001 -,--- -,---

S5:

-,---

S6:

S5,000 S6,001

S7:

-,--- -,---

-, --- S7, 100;

-,--- -,---

```

Figure 3: Asynchronous flow table for **DME-FAST-E**

state encoding or multi-output logic minimization. <sup>2</sup> Further, its Lisp implementation and slow algorithms for state minimization and logic minimization severely limit its usefulness. Finally, it does not allow fed-back outputs, missing an opportunity to significantly reduce implementation complexity.

The 3D system, presented in [38][40][39], also synthesizes two-level implementations, but accepts extended burst-mode specifications — a larger class of specifications than either UCLOCK or MINIMALIST (at present) handle. Unlike UCLOCK, 3D uses fed-back outputs; unlike MINIMALIST, their use is not an option: it is required. In contrast to MINIMALIST, it uses heuristic greedy state minimization and encoding algorithms. It also always performs exact single-output logic minimization (using HFMIN [11]), to produce reasonably high-performance implementations. Even so, none of its methods (save HFMIN) offers any guarantee of optimality; benchmarks show that MINIMALIST's algorithms give better results.

Finally, whereas both UCLOCK and 3D support only a single implementation style and one cost function, MINIMALIST supports *multiple* implementation styles and cost functions. MINIMALIST thus allows designers to explore various trade-offs and choose the implementation which best suits their application.

## 2.4 Comparative Overview: MINIMALIST vs. Previous Tools

The following table provides an overview of the choices available in the most important dimensions of the solution space for Minimalist and the two competing burst-mode synthesis toolkits, 3D and Uclock. Each dimension is correlated with the relevant operating mode or tool option, which will be defined later in this paper.

| synthesis pkg | fed-back outputs     | state-min | code length          | type of logic          | cost func             |

|---------------|----------------------|-----------|----------------------|------------------------|-----------------------|

|               | (machine impl style) |           | (constr. sat. mode)  | (logic impl. style)    |                       |

| Uclock        | non-fed-back only    | exact     | one solution         | single-output only     | products              |

| 3D            | fed-back only        | heuristic | one solution         | single-output only     | literals†             |

| Minimalist    | both                 | both      | many solutions       | single-, multi-output, | $\operatorname{both}$ |

|               |                      |           | (varied code length) | or output-disjoint     |                       |

<sup>†</sup> In the original 3D implementation, the sole cost function was product count.

<sup>&</sup>lt;sup>2</sup>In practice, critical race-free codes for UCLOCK were produced either manually, or using auxiliary programs.

## 3 MINIMALIST Framework

The Minimalist framework consists of several key pieces: core data structures, a class and algorithm library, and an extensible interpreter, implemented in roughly 45,000 lines of C++ (including several of the core tools, e.g. Hfmin and Chasm).

The MINIMALIST framework incorporates a simple set of C++ classes to represent the original burst-mode specification. Early synthesis steps such as state minimization and state encoding simply transform or place annotations on these structures. As a result, additional steps or transformations are easily accommodated.

To assist in implementing new synthesis algorithms, MINIMALIST offers class libraries for manipulating both asynchronous burst-mode specifications, two-level logic (hazard- and non-hazard-free), dichotomies, unate and binate covering problem instances, arbitrary-length bitstrings, and the like. To facilitate interfacing to external programs, a small number of basic translators to common formats (e.g. Berkeley PLA or BLIF) is incorporated.

Finally, MINIMALIST provides a shell-like interpreter, extensible with commands written in C or C++. The interpreter supports user-defined shell functions, on-line help, command- and filename-completion, variables, control constructs (loops, conditionals), arithmetic, external process invocation, input/output redirection, and the like. Also, functionality can be augmented by dynamically-loaded code, without having to re-link the executable.

The result is a uniquely flexible, potent context for integrating synthesis tools, that we find lacking in existing packages [23][38].

## 4 MINIMALIST Tools

The following sections describe the set of synthesis, verification and testability tools currently incorporated into the Minimalist toolkit. Work is currently under way to integrate other existing high-quality tools such as technology mapping [14, 1, 2] and timing analysis [4], taking advantage of Minimalist's plug-in framework. With these additions, Minimalist will offer an even more capable path for asynchronous synthesis and verification.

#### 4.1 State Minimization

MINIMALIST includes two new and very efficient algorithms for exact state minimization. In contrast, the 3D method uses a heuristic greedy minimization algorithm. Therefore, in this section, we will focus on a more direct comparison: the MINIMALIST exact algorithms and an earlier exact state minimization algorithm found in UCLOCK.

MINIMALIST improves significantly on UCLOCK's state minimization approach in two ways — (i) by allowing outputs to be fed back as inputs, and (ii) by dramatically reducing run-time complexity.

MINIMALIST offers two new exact state minimization algorithms: 1) for implementations without fedback outputs (loosely based on UCLOCK's method), and 2) for implementations with fed-back outputs. The latter is the first exact algorithm for state minimization that handles fed-back outputs. Thus, it supports two machine implementation styles. As mentioned earlier, fed-back outputs can dramatically reduce the implementation's logic complexity.<sup>3</sup> In particular, their use allows merging certain states which would otherwise be incompatible. MINIMALIST makes use of this fact by relaxing UCLOCK's compatibility relation. In fact, several benchmark specifications collapse into a single state using the new relation, whereas UCLOCK's relation results in 2 or more states.

<sup>&</sup>lt;sup>3</sup>See the benchmark results.

Second, Minimalist improves run-time by several orders of magnitude over the Uclock method. Uclock uses an expensive algorithm to generate maximal compatibles. In contrast, Minimalist uses a simple transformation which allows it to generate maximal compatibles using a fast unate prime generation algorithm instead. In addition, both Uclock and Minimalist (currently) approximate the binate covering step by a unate one followed by a closure check<sup>4</sup>. Uclock, however, employs Petrick's method to solve the unate problem, while Minimalist employs a state-of-the-art tool, mincov [27]. The combination of these two algorithmic enhancements reduce the run-time of state minimization by two or more orders of magnitude. To date we have encountered only one specification for which state minimization requires more than a few seconds, whereas run-times of many minutes were common for Uclock. For such large specifications, both of Minimalist's algorithms also feature an approximate mode which further reduces run-time.

#### 4.2 CHASM

For state encoding, MINIMALIST uses CHASM (Coding for Hazard-free Asynchronous State Machines), the first exact method for input encoding of multiple-input change asynchronous machines. CHASM has many operating modes. One highlight is that its "exact mode" can be used to produce exactly optimum two-level output logic, over all critical race-free encodings, thus optimizing the key performance parameter for asynchronous networks (output latency). Its approximate mode also gives significant reductions in overall implementation cost.

Chasm, as reported in [11], loosely follows the flow of the Kiss [9] method for input encoding of synchronous machines. Several significant modifications are required to handle asynchronous machines. There are three steps. First, symbolic hazard-free logic minimization is performed. Second, a set of encoding constraints is generated, which properly subsumes both the classic synchronous Kiss ("face embedding") optimality constraints as well as asynchronous critical race-free [35] constraints. The constraints are in the form of generalized dichotomies [35] (not face embedding constraints). Finally, the constraints are solved. For constraint solution, Chasm has two modes: (i) an exact mode, which uses DICHOT [30], and (ii) an approximate mode, using Nova's [37] simulated annealing engine. The approximate mode, as in Nova, attempts to solve as many constraints as possible, under the restriction of a fixed code length; it has the advantage that it may reduce next-state logic complexity.

For MINIMALIST, CHASM has been extended in several new ways.

First, Chasm is now being applied to implementations with fed-back outputs. Specifically, we have proven that Chasm requires no modification to properly encode implementations with fed-back outputs. A modified functional specification is provided as input, which simply identifies the primary outputs as fed-back inputs. The symbolic two-level logic minimizer then forms a symbolic cover on this new function.

Second, Chasm can now target three **logic implementation styles**: (i) multi-output (where outputs and next-state may share products), (ii) output-disjoint (where products are shared among outputs, but not between outputs and next-state), and (iii) single-output (where no product terms are shared between any output functions). The motivation is that the "single-output style" is most suitable for performance-optimal designs: each output is individually optimized. Note that, in asynchronous machines (unlike synchronous), output latency is often the key parameter to overall system performance in a network of interacting machines. The "multi-output style" is most suitable for area-optimal designs, since it uses maximal sharing of logic. Finally, the "output-disjoint style" is a balanced compromise.

For modes (ii) and (iii), a novel feature of Chasm is that it produces exactly optimum two-level output logic, over all critical race-free encodings. This result holds, because the optimal output-only state encoding problem is a true "input encoding problem", unlike the general optimal state encoding problem (which is

<sup>&</sup>lt;sup>4</sup>We have yet to see the closure check fail, due in part to the manner in which the set of state compatibles is refined to a partition.

an approximation).

Finally, Chasm targets two distinct **cost functions:** (i) product cardinality, and (ii) literal count, at the symbolic level. It does the latter by performing weighted unate covering during symbolic logic minimization. This technique is only a heuristic, however, because the literal count of the final binary cover can only be estimated. In practice, the heuristic nonetheless yields significant reduction in literal count.

## 4.3 HFMIN

After state minimization and encoding, MINIMALIST performs two-level hazard-free logic minimization. This step is normally performed using HFMIN, the first exact multi-output symbolic hazard-free two-level logic minimization tool.

HFMIN, as reported in [11], uses Espresso to generate ordinary prime implicants, then refines them as needed to dynamic hazard-free (DHF) primes [24], and finally, performs a unate covering step using MINCOV [28], covering required cubes [24] in lieu of minterms. HFMIN's use of such highly-optimized algorithms for sub-steps allows it to readily handle most minimization problems we have encountered.

HFMIN has also been enhanced for MINIMALIST with the ability to produce output-disjoint<sup>5</sup> and single-output covers, and the ability to minimize literal count. Output-disjoint and single-output covers are formed by generating a suitable set of prime implicants before DHF refinement takes place. The rest of the algorithm proceeds unchanged.

To minimize literal count, HFMIN performs a weighted unate covering step where prime implicants are assigned weights according to their literal count. In addition, HFMIN now supports a limited post-processing step that further reduces literal count. This step is similar in spirit to the *make-sparse* operation of Espresso [28]. A single pass is made over each selected prime implicant, removing output literals as long as the result remains a valid (hazard-free) cover. The input portion is then expanded, if possible. Unlike *make-sparse*, our current method makes no guarantee that the resulting product is maximally expanded. Nonetheless, despite its simplicity, the operation often yields significant reductions in literal count.

HFMIN is now widely used in several other burst-mode CAD packages, including the 3D method [38] and ACK [16]. It has also been used as part of the asynchronous tool suite at Intel Corporation, where it has been applied in the design of a high-speed experimental asynchronous Instruction-Length Decoder (see [5]).

## 4.4 ESPRESSO-HF

For very large problems which HFMIN is unable to solve in reasonable time, MINIMALIST offers ESPRESSO-HF [33], a new fast heuristic two-level logic minimizer. ESPRESSO-HF uses an algorithm loosely based on ESPRESSO (but substantially different from it), to solve problems with up to 32 inputs and 33 outputs. On benchmark examples, ESPRESSO-HF can find very good covers — at most 3% larger than a minimum-size cover — in less than 105 seconds. For typical examples, ESPRESSO-HF obtains an exact or near-exact result in under 3 seconds.

Currently, Espresso-HF only implements multi-output minimization targetting product cardinality, and so it is normally used only for designs which exceed Hfmin's capacity. However, output-disjoint or single-output minimization can easily be implemented by a trivial modification of the code, and will be available in future releases of Minimalist.

#### 4.5 IMPYMIN

IMPYMIN [34] is a new state-of-the-art fully-implicit exact two-level hazard-free logic minimizer. It greatly exceeds the capacity of previous exact tools (e.g. HFMIN), minimizing very large multi-output functions,

<sup>&</sup>lt;sup>5</sup>products are shared among outputs, but not between outputs and next-state

including some for which no exact result had previously been obtained. Run-times are typically under 16 seconds. The most difficult problem available, with 32 inputs and 33 outputs, had never before been solved exactly, but required only 813 seconds using IMPYMIN.

Both Espresso-HF and Impymin can solve all currently-available benchmark examples, including several which have not been previously solved. For larger examples that can be solved by Hfmin, these two minimizers are typically several orders of magnitude faster.

## 4.6 Synthesis-for-Testability

MINIMALIST incorporates a recent method [26] for synthesis-for-testability targetting multi-level logic. The method produces circuits that are both hazard-free and 100% testable under either stuck-at or robust path delay fault models, with little or no overhead. First, it uses a novel two-level hazard-free logic minimization algorithm which minimizes the number of redundant cubes, as well as the number of non-prime cubes. (The tool currently operates only in single-output mode.) This helps maximize testability without using additional inputs. If not yet completely testable, the circuit is converted to a multi-level form which is completely testable (if possible). If still not completely testable (rarely the case), controllable inputs are added, yielding 100% testable logic. Finally, hazard- and testability-preserving multi-level transformations are used to reduce the area of the resulting circuit. The area overhead is typically zero, and in all cases is less than 10% [26].

## 4.7 Verifier

MINIMALIST features a simple tool to verify that a given logic implementation (produced by any method) realizes the specified burst-mode behaviour, independent of the particular state merges or encoding which have been performed. The verifier simulates the implementation's response to each specified input burst, and compares it to the specification; any mismatches of output or state at the end of the burst and any logic hazards are reported. Although each burst is considered only once, the analysis that is performed accounts for all possible interleavings of individual input changes. Since the verifier needs to traverse each edge in the specification's state graph only once, this tool is eminently practical even for very large specifications—the time required is never more than a few seconds. Currently, verification of only two-level AND/OR implementations is provided. However, the framework allows for verification of multi-level implementations as well (using the 9-valued algebra developed by Kung [17]), which will be completely supported in the near future. Also, the current version of the verifier does not detect output changes made after partial input bursts. Finally, being a purely combinational verifier, it does not verify the one-sided timing constraints also needed to ensure correct operation [3]. Such a capability may be added in a future release.

## 5 A Synthesis Session

| \$ MinShell minimalist> help         |                |             | # Sta         | art the MINIMALIST shell # Show list of commands |

|--------------------------------------|----------------|-------------|---------------|--------------------------------------------------|

| assign-states                        | break          | call        | cd            |                                                  |

| continue                             | define         | echo        | expr          |                                                  |

| for                                  | help           | if          | impymin-logic |                                                  |

| make-testable                        | min-logic      | min-states  | pwd           |                                                  |

| quit                                 | read-spec      | set         | set-encoding  |                                                  |

| set-state-cover                      | show-encoding  | show-logic  | source        |                                                  |

| verify-logic                         | while          | write-flow  | write-instant |                                                  |

| write-spec                           | write-symbolic | write-trans |               |                                                  |

| minimalist> $pwd$ /u/minimalist/demo |                |             |               | # Show current directory                         |

```

# Run 'ls'

minimalist> ls

bin ex lib

minimalist> ls ex

dme-e dram-ctrl

pe-send-ifc scripts

stetson

dme-fast-e hp-ir

pscsi

scsi-iccd92

# Move to another directory

minimalist> cd ex/dme-e

minimalist> ls

dme-e.bms

# Show syntax of 'read-spec'

minimalist> help read-spec

read-spec [-v] <file> [<spec-var>]

Read the Burst-Mode specification in <file> and store it in <spec-var>,

or, if <spec-var> is not specified, 'theSpec'.

\# Read the Burst-Mode specification

minimalist> read-spec dme-e.bms

Specification passed validity check.

Specification has 3 inputs, 3 outputs, and 8 states.

minimalist> plot graph dme-e.bms

[... a window displays the burst-mode graph; press Ctrl-Q or the Quit button to dismiss it ...]

minimalist> min-states

# Perform state minimization

*** Performing state minimization... ***

State cover: { { SO S1 S4 }, { S2 S3 }, { S5 S6 S7 } }

Machine has 3 states after minimization.

minimalist> assign-states -F

# Assign states with a CRF encoding

No encoding style specified; defaulting to critical race-free

*** Performing state assignment... ***

Invoking 'chasm' as 'chasm -C DME_E-F.func DME_E-F.trans'

*** Machine encoded by CHASM ***

State SO': 11

State S1': 10

State S2': 00

# Produce the logic implementation

minimalist> min-logic -F -L

*** Performing logic minimization... ***

Invoking 'hfmin' as 'hfmin -P -C -l -S -o DME_E-FL.sol DME_E-FL.pla DME_E-FL.btrans'

*** Final PLA ***

# PLA file for machine DME_E-FL

.i 8

.o 5

.ilb LIN RIN UIN LOUT_i ROUT_i UOUT_i YO Y1

.ob y0 y1 LOUT ROUT UOUT

.type fr

.р 7

10----1 00010

-01---1 00010

-0----1 01000

10----0 10100

00----1- 11000

--0---1- 10000

-01---0 00001

Total number of literals: 28

Number of products:

```

```

Number of products implementing outputs:

4 Literals in products implementing outputs: 17

Literals in products implementing next-state: 16 Average literals per output:

5.66667

Result stored in 'DME_E-FL.sol'.

# Verify the implementation

minimalist> verify-logic -F -L

Using logic implementation stored in 'DME_E-FL.sol'.

*** Starting Burst-Mode machine simulation. ***

*** Implementation verified successfully! ***

minimalist> plot graph DME E-FL.sol

# Display the implementation

[... a window displays the 2-level logic; press Ctrl-Q or the Quit button to dismiss it ...]

# Run the above synthesis steps using a script

minimalist> source ../scripts/script-FBO.MOL-CRF dme-e.bms

[... same results as above, without interaction ...]

minimalist> quit

```

## 6 Results

This section compares synthesis results using MINIMALIST to those using the preeminent burst-mode asynchronous synthesis paths, namely 3D [38] and UCLOCK [23]. We highlight MINIMALIST's unique ability to support various cost metrics and implementation styles by showing several different experiments. For each, we indicate the cost function which we target, and the corresponding settings of MINIMALIST's modes.

## 6.1 Experimental Set-up

The benchmark suite consists of 23 burst-mode circuits, including several industrial designs, as well as a number of large asynchronous machines (e.g., see sc-control and oscsi). The circuits it-control, rf-control, sc-control, and sd-control are part of a low-power infrared controller designed at HP Labs as part of the Stetson project [20]. pe-send-ifc and sbuf-xxx-ctl, also from HP Labs, are part of a high-performance adaptive routing chip, used in the Mayfly parallel processing system [32]. Several others (e.g. the scsi-xxx and pscsi-xxx suites) come from a high-performance asynchronous SCSI controller designed by Yun while at AMD [41]. A DRAM controller circuit for Motorola 68K processors [38], dram-ctrl, completes the suite.

All MINIMALIST results are the best of a very small number of trials using fixed-length encodings. Generally, near-minimum code lengths are used. Here, minimum length refers to the smallest length sufficient for a critical-race free encoding, which is necessary to ensure correct operation. However, as demonstrated below, a trade-off exists, whereby significantly wider encodings sometimes offer better output logic at the expense of added next-state logic complexity. Hence, the results below occasionally make use of longer codes.

Run-times for the complete synthesis path are comparable for all tools (MINIMALIST, 3D, and UCLOCK), ranging from under 1 second to several minutes for the largest designs.

#### 6.2 Performance-Oriented Comparison with 3D

The first experiment (shown in Table 1) shows synthesis results using both MINIMALIST and 3D for a performance-oriented implementation.

For asynchronous burst-mode machines, the metric that best approximates performance is *output latency*. In an asynchronous system, unlike synchronous, the input-to-output latency typically determines a machine's performance, as well as overall system performance. State changes are not bound to a clock period, and in practice are usually non-critical (see [20]).

```

define syn_FBO_so_lit { specFile codeLen } { # Single-output, optimize lit count

read-spec $specFile

min-states -F

assign-states -F -s -L -O -l $codeLen

min-logic -F -s -L

verify-logic -F -s -L

}

call syn_FBO_so_lit dram-ctrl.bms $codeLen

```

Figure 4: Performance-oriented synthesis script for MINIMALIST

Based on the above observation, we now indicate the settings of the various modes of MINIMALIST for this experiment. In the context of technology-independent two-level logic, the cost function that most reasonably approximates output latency is the average number of literals per output. When comparing two results for the same machine (so that the number of outputs is fixed), this cost is equivalent to total output literal count, so this is used instead.

Roughly half of the MINIMALIST results in this set of runs make use of the **fed-back output machine implementation style**. Table 1 identifies the particular style chosen for each design in the column labelled 'FBO'. MINIMALIST is directed to use the **single-output** logic implementation style, and the **literal count** cost function. This combination of modes best minimizes average output literal count. This cost function also allows for a fair comparison to 3D, which produces single-output logic with minimal literal count. Finally, the encoding step uses **fixed-length constraint satisfaction** mode, attempted under several code lengths.

The MINIMALIST script in Figure 4 summarizes the selected modes. The script is parameterized by code length, using the variable \$codeLen, and proceeds as follows. First, the specification is read from a file and checked for validity. Next, the machine is subjected to exact state minimization using fed-back outputs. The states are encoded using Chasm, with the fed-back output ('-F'), single-output ('-s'), literal-count ('-L'), and fixed-length ('-1') flags. The final two-level logic is then synthesized using Hfmin, again passing the single-output and literal-count flags. Finally, the resulting logic is verified using the algorithm sketched in Section 4. The script was run in batch mode several times. The run having the lowest output literal count over 1-3 code lengths near the minimum is reported.

The 3D results were obtained using the 3D tool on the Unix platform. Unlike MINIMALIST, 3D embodies a hard-wired synthesis path, and produces a single deterministic result. Specifically, 3D first performs heuristic state minimization, followed by heuristic state encoding, and finally, exact two-level single-output logic synthesis using HFMIN, targetting total literal count. Thus, a single run for each design gives the reported (and the only possible) result.

Table 1 summarizes the comparison. MINIMALIST synthesis results demonstrate an average reduction of 11% in *output literals*, with the best being a 37% reduction for sd-control. In exchange for MINIMALIST's simplification in output logic, an increase in total literal count is occasionally observed (see for example pe-send-ifc and pscsi-tsend). However, MINIMALIST also frequently achieves a reduction in *total literal count* as well, with larger designs such as stetson-p1 and oscsi among the most impressive gains (38% and 25%, respectively).

Clearly, MINIMALIST's gains come in part from its ability to explore wider encodings. In fact, in 12 of the 23 designs, the best result is seen at a longer code length than 3D uses. The greatest improvement overall, in sd-control, is seen at a significantly longer code length — 7 bits for MINIMALIST vs. 3 bits for 3D. For two designs, MINIMALIST chooses a shorter encoding than 3D: dram-ctrl (whose 0-bit encoding is enabled by the use of fed-back outputs), and oscsi (where 3D curiously uses 7 bits, despite no gain

<sup>&</sup>lt;sup>6</sup>A nearly identical script exists in which all steps do not make use of fed-back outputs.

in output literals and a considerable increase in overall logic complexity). For the remaining examples, MINIMALIST achieved its best result at the same code length as 3D.

## 6.3 Area-Oriented Comparison with 3D

Our second experiment (also shown in Table 1) shows the results of an **area-oriented comparison** of Minimalist and 3D.

The cost metric that best approximates area for technology-independent two-level logic is total literal count; hence, total literal count is used in this comparison.

Based on the above observation, we now indicate the settings of the various modes of MINIMALIST for this experiment. The vast majority of the MINIMALIST results in this set of runs use the **fed-back output** machine implementation style. Again, the table identifies the particular style chosen for each design. Throughout, MINIMALIST is directed to use the **multi-output** logic implementation style, and the **literal count** cost function, which best minimizes total literal count. Finally, the encoding step uses **fixed-length constraint satisfaction** mode.

These runs were obtained using a script identical to that of Figure 4, but using the multi-output logic implementation style. In particular, the single-output ('-s') flag was removed from the state encoding and logic minimization steps. Again, the cost function used was total literal count.

As shown in Table 1, MINIMALIST's term-sharing across outputs and next-state provides for significant reductions in total area. MINIMALIST's results for the area-targetted run show an average reduction of 33% in total literal count over 3D, the best being 48% for sc-control. For all designs, MINIMALIST achieved strictly better results than 3D. Although these runs did not target product count directly, they offer similarly dramatic reductions by that metric as well. An average of 42% improvement is observed, the best being 57% for sc-control. Again, MINIMALIST's results are strictly better than 3D in every case.

Unlike the performance-targetted runs, the code length used by MINIMALIST rarely exceeded that of 3D (only 3 times out of 23 designs), and never by more than 1 bit. In fact, MINIMALIST uses slightly fewer total state bits over the entire benchmark suite than does 3D, by roughly 5%.

## 6.4 Area-Oriented Comparison with UCLOCK

The final comparison, in Table 2, shows synthesis results for UCLOCK (as reported in [11]) and MINIMALIST. For a fair and interesting comparison, we plugged some of the MINIMALIST tools into the UCLOCK path, to isolate and highlight two differences: (i) machine implementation style (choice of fed-back vs. no fed-back outputs), and (ii) state minimization algorithms. Even though UCLOCK does not use any optimal state assignment algorithms, we attached CHASM and HFMIN as a back end, to isolate these front-end differences. We also limited MINIMALIST to the only logic minimization modes that are available in UCLOCK: the cost function is **product cardinality**, and the logic implementation style is **multi-output**.

Table 2 shows the experimental results. In both MINIMALIST and the "improved" UCLOCK, reported results are the best of several fixed-length trials at or near the minimum code length. The majority of the MINIMALIST results use the **fed-back output** machine implementation style.

Not surprisingly, many MINIMALIST and UCLOCK results are nearly identical, since the operating modes are very similar. However, MINIMALIST's use of fed-back outputs results in significant gains in several cases (e.g., dram-ctrl and scsi-isend-bm). In addition, MINIMALIST obtains synthesis results in several cases where UCLOCK failed to complete, again due in part to MINIMALIST's more capable state minimization method.

A performance-oriented comparison to UCLOCK (like the above comparison to 3D) is possible, but is omitted, due to space considerations.

| design         j/s/o         codelon         prod/mance (single-output)         performance (single-output)         area (multi-output)           design         j/s/o         codelon         prod/s         lts         outlits         FBO         codelon         prods           deran-ctr         7/12/6         1         21         71         37         √         0         17         57         √         0         17         37         √         0         17         37         √         0         17         37         √         0         17         37         √         0         17         37         √         0         17         37         √         0         17         37         √         0         17         37         √         0         17         37         √         3         11         38         √         3         11         18         3         18         5         4         3         11         18         3         18         5         4         3         11         18         4         3         11         18         4         3         11         18         4         3         11         18         4 <th></th> <th></th> <th></th> <th>3D</th> <th></th> <th></th> <th></th> <th></th> <th></th> <th>M</th> <th>MINIMALIST</th> <th><math>\mathbf{Z}</math></th> <th></th> <th></th> <th></th> |                |          |         | 3D    |      |         |              |          |                        | M         | MINIMALIST | $\mathbf{Z}$ |         |           |                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------|---------|-------|------|---------|--------------|----------|------------------------|-----------|------------|--------------|---------|-----------|-----------------------|

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |          |         |       |      |         |              | performs |                        | le-output | (          |              |         | ti-output | (                     |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | design         | i/s/o    | codelen | prods | lits | outlits | FBO          | codelen  | $\operatorname{prods}$ | lits      | outlits    | FBO          | codelen | prods     | $\operatorname{lits}$ |

| 4/6/3 $2$ $13$ $44$ $30$ $3$ $14$ $46$ $26$ $31$ $44$ $46$ $46/6/3$ $44/6/3$ $44$ $46/6/3$ $44/6/3$ $44$ $46/6/3$ $44$ $46/6/3$ $44/6/3$ $44$ $46/6/3$ $44$ $46/6/3$ $44$ $46/6/3$ $44$ $46/6/3$ $46/6/3$ $46/6/3$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$ $41/10/4$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | dram-ctrl      | 7/12/6   | 1       | 21    | 7.1  | 22      | >            | 0        | 17                     | 22        | 22         | >            | 0       | 14        | 51                    |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | pscsi-ircv     | 4/6/3    | 2       | 13    | 44   | 30      |              | က        | 14                     | 46        | 50*        |              | ಣ       | 10        | 38*                   |

| $4/9/3$ $4$ $31$ $105$ $44$ $6$ $31$ $111$ $38$ $\checkmark$ $3$ $18$ $4/10/3$ $4$ $2$ $77$ $41$ $7$ $31$ $116$ $35$ $\checkmark$ $3$ $18$ $4/1/4$ $3$ $4$ $2$ $4$ $7$ $2$ $17$ $3$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$ $4$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | pscsi-trcv     | 4/6/3    | П       | 10    | 35   | 30      |              | 2        | 13                     | 43        | 27         | >            |         | 2         | 30                    |

| $4/10/3$ 4         22         77         41         7         31         116         35 $\checkmark$ 3         18 $4/7/4$ 2         18         58         45 $\checkmark$ 2         17         58         43 $\checkmark$ 3         18 $4/10/4$ 3         24         86         43 $\checkmark$ 2         17         58         43 $\checkmark$ 3         16 $3/7/3$ 1         7         22         17         5         15 $\checkmark$ 3         16 $\checkmark$ 3         17         3         4                                                                                                                                                                                                                                                                                                                                                                                                                                                             | pscsi-isend    | 4/9/3    | 4       | 31    | 105  | 44      |              | 9        | 31                     | 111       | 38         | >            | က       | 18        | 29                    |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | pscsi-tsend    | 4/10/3   | 4       | 22    | 22   | 41      |              | 7        | 31                     | 116       | 35         | >            | က       | 18        | 99                    |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | pscsi-trcv-bm  | 4/7/4    | 2       | 18    | 58   | 45      | >            | 2        | 17                     | 58        | 43         | >            | 2       | 11        | 45                    |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | pscsi-tsend-bm | 4/10/4   | 3       | 24    | 98   | 43      |              | 7        | 31                     | 118       | 43         | >            | ಣ       | 16        | 63                    |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | sbuf-read-ctl  | 3/7/3    | 1       | 7     | 22   | 17      |              | 2        | 6                      | 56        | 15         | >            | П       | 9         | 21                    |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | spuf-send-ctl  | 3/8/3    | 2       | 17    | 51   | 32      |              | က        | 14                     | 41        | 24         |              | 2       | 11        | 36                    |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | pe-send-ifc    | 5/11/3   | 2       | 24    | 89   | 56      |              | 20       | 32                     | 136       | 55         | >            | က       | 18        | 88                    |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | scsi-isend-bm  | 5/10/4   | 2       | 26    | 87   | 59      | >            | 2        | 23                     | 92        | 99         | >            | 2       | 17        | 63                    |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | scsi-isend-csm | 5/8/4    | 2       | 22    | 99   | 44      |              | 2        | 18                     | 53        | 41         |              | 2       | 12        | 49                    |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | scsi-trcv-bm   | 5/10/4   | 2       | 24    | 78   | 50      | >            | 2        | 22                     | 71        | 50         | >            | 2       | 17        | 64                    |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | scsi-trcv-csm  | 5/8/4    | 2       | 21    | 64   | 42      |              | 2        | 18                     | 52        | 40         |              | 2       | 12        | 46                    |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | scsi-tsend-bm  | 5/11/4   | 2       | 28    | 92   | 29      |              | 4        | 24                     | 98        | 48         |              | ಣ       | 19        | 75                    |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | scsi-tsend-csm | 5/10/4   | 2       | 20    | 22   | 41      |              | 9        | 24                     | 22        | 34         | >            | 2       | 14        | 52                    |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | it-control     | 5/10/7   | П       | 21    | 73   | 56      | >            |          | 19                     | 89        | 99         | >            |         | 13        | 54                    |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | rf-control     | 6/12/5   | 2       | 12    | 44   | 34      |              | ಸಂ       | 15                     | 29        | 30         | >            | 2       | 11        | 43                    |